# Analysis and Behavioral Study of Substrate Noise Coupling in Silicon Integrated Circuits

Mandeep Kaur, Rajesh Mehra

**Abstract-** In this paper the behavioral study is presented on uniformly doped silicon substrate. Resistivity and thickness of substrate is varied and analyzed. It is observed that with the increase in resistivity and decrease in thickness of substrate, crosstalk problem existing in mixed circuits is reduced. FEM technology is used and HFSS simulation is done for S parameter extraction for 1000\*1000\*tµm<sup>2</sup> sized substrate with two square contacts of size 50\*50µm<sup>2</sup>, where't' refers to thickness of substrate.

Key Words: Substrate, substrate noise, coupling, finite element method, doping, resistivity, parasitic elements, isolation, HFSS.

#### **1** INTRODUCTION

Single chip mixed signal designs combining digital and RF/analog blocks built over a common substrate provide reduced levels of cost, power dissipation and smaller package count. However its disadvantage is that the important fault introduced is substrate noise. Substrate noise isolation is getting more and more difficult to handle with new and upcoming technologies .With the increase level of integration in IC's today and increase in digital circuits speed, the problem of substrate is becoming more and more prominent. The performance of overall chip degrades. This problem is observed during testing phase only after chip is fabricated. Substrate noise determination can reduce the turnaround time for circuits and prevent costly design. In a lightly doped substrate, this analysis of the substrate noise problem is divided into three aspects [1], i.e., generation, propagation, and impact of substrate noise. In this paper a behavioral study of coupling in a common silicon substrate is presented. This paper also shows dependence of cross talk on substrate contact separation, substrate thickness. Substrate resistivity and signal frequency.

## **2 FINITE ELEMENT METHOD**

The finite element method subdivides the entire domain into triangular (2D) or tetrahedral (3D) elements and

treats the elements as linear. The resulting linear relations between the potentials at the corners of the elements (the FEM nodes) can then be expressed by a piecewise linear (or piecewise planar for 3D) function. This linear function implies that every edge in the FEM discretization represents a resistance. In other words, the FEM discretization is equivalent to a resistance network. The resulting network is large and sparse. However, only a small number of the FEM nodes are actually terminal nodes, while the rest of the FEM nodes are internal nodes. Only the terminal nodes are connected to other physical structures (e.g. transistors, vias or possibly a parasitic interconnect capacitance). Therefore, the FEM network will have to be solved such that the internal nodes are eliminated and only the resistances between the terminal nodes remain. As such, the FEM can be very accurate and flexible. Even though it is possible to use the FEM in such cases, its limited speed might be prohibitive, especially for larger-scale modeling problems. A substrate is a medium composed of several conductive layers. A deposition process is done using appropriate materials on the top of these layers. The ports or contacts correspond to lightly doped but strongly conductive areas [8].

## 3 HFSS

"HFSS is the industry-standard software for Sparameter, full-wave SPICE extraction and electromagnetic simulation of high-frequency and highspeed components. HFSS is widely used for the design of on-chip embedded passives, PCB interconnects, antennas, RF/microwave components, and highfrequency IC packages. HFSS improves engineering productivity, reduces development time, and better assures first-pass design success.

The latest release of HFSS delivers significant productivity gains to Microwave/RF engineers and expands electromagnetic co-design to a new segment of engineers working in the areas of RF/analog IC and multi-gigabit designs as well as EMI/EMC.HFSS uses the Finite Element Method (FEM) to solve Maxwell's equations.

The primary advantage of the FEM for solving partial differential equations lies in the ability of the basic building blocks used to discretize the model to conform to arbitrary geometry. The arbitrary shape of the basic building block (tetrahedron) as shown in Fig.1 also allows HFSS to generate a coarse mesh where fewer cells are needed to yield an accurate solution, while creating a finely discretized mesh where the field is rapidly varying or higher accuracy is needed to obtain an accurate global solution.

The FEM has been a standard for solving electromagnetic problems since the inception of HFSS in 1990. The FEM has been a standard for solving problems in structure mechanics since the mid 1950's.

Fig.1 Tetrahedron shape of mesh

Substrate coupling occurs in integrated circuits due to the conductive and capacitive path which exists in the silicon substrate. Conductive path of silicon substrate is predominant at low frequencies, while the capacitive

path becomes significant at high frequencies. Noise is injected into the substrate through resistive injection (e.g. impact ionization current and ohmic guarding) and capacitive injection (e.g. junction capacitance). Substrate noise reception mainly takes place through capacitive sensing (i.e. junction capacitances). Substrate noise, usually generated by noisy circuit block (i.e. digital block), received by sensitive analog/RF blocks can severely degrade its performance, thus degrades the performance of the overall system. There are quite a few substrate crosstalk suppression techniques that have been widely implemented on industrial level. Guard ring is one of the most common techniques used, where *p*+ silicon substrate ring provides low impedance return path for the substrate noise towards the ground. Similarly, buried layer and triple-well isolation are used in BiCMOS and CMOS processes, respectively. Instead of using low resistivity substrate, a piece of silicon substrate can be modeled by an RC network, where the R and C depend on the substrate resistivity and dielectric constant, respectively. While the capacitance takes effect at relatively high frequencies, the resistance is dominant at low frequencies. The high-resistivity substrate can improve the isolation below the cut-off frequency but starts to lose its isolation effectiveness at earlier stage which makes it less suitable for highfrequency1 application with respect to isolation, not to mention the higher cost of high-resistivity silicon substrates.

#### **4 MODELING OF SUBSTRATE COUPLING**

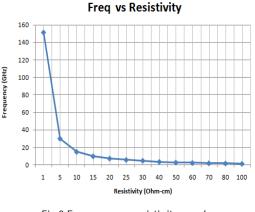

The numerical modeling using the device solver requires considerable computational time. Therefore, it is desirable to build an equivalent circuit model comprised of ideal lumped elements. The equivalent circuit can be solved using common circuit simulators (e.g. SPICE, ADS). Modeling substrate noise coupling is very complex since it includes all noise injectors and receptors built on a particular substrate .substrate doping can vary from 1S/m to 10000S/m. 10S/m is for lightly doped substrate and 10000S/m for heavily doped  $f_c = \frac{1}{2\pi\rho_{sub}\varepsilon_{Si}}$  It is 15Ghz for lightly doped substrates .So frequency<15Ghz substrate behave resistively and capacitance is prominent at frequencies >15Ghz [4]. Frequency vs Resistivity curve is shown in Fig.2, which shows that frequency is inversely proportional to resistivity of substrate

Fig.2 Frequency vs resistivity graph

But it is clear that on such substrates reactance cannot be ignored with RF frequencies. For higher frequencies inductive skin effect and slow wave effect can rise. Here we have considered uniformly distributed substrat. This paper is limited to behavioral analysis of a substrate with small number of contacts i.e. two. Contact areas are where circuit interacts with substrate. Equipotential assumption is valid until contact is not too large. Contacts interact without direct coupling but with resistance they are still indirectly coupled. The device to substrate junctions are considered as eqipotential contacts with surface. Substrate has distributed impedance. Substrate provides a parasitic coupling path for signals within same circuit. Highly mixed circuits provide crosstalk.

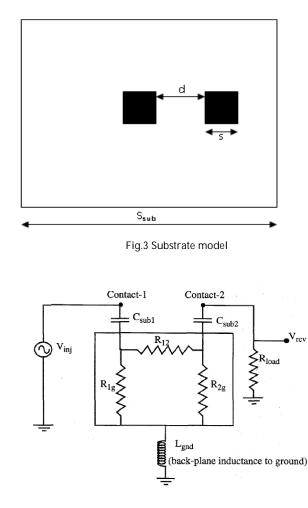

In this paper, model consist of two metal substrate contacts of size 50\*50  $\mu m^2$  and silicon substrate of size 1000\*1000  $\mu m^2$  with variable thickness of 50, 100, 500, 1000  $\mu m$  as shown in Fig.3, where d is the distance between two contacts, s is the size of contact and S<sub>sub</sub> is the size of substrate.

#### Fig.4 Equivalent circuit model

Fig.4 represent equivalent circuit model where  $R_{12}$  is resistance between two contacts,  $R_{1g}$  and  $R_{2g}$  are resistance between ground and contact [2].

HFSS use FEM to solve the field equations in a volume. It does not solve carrier continuity equations. The substrate coupling is represented in terms of isolation between contacts [5]. This isolation depends on several factors besides substrate model elements. These include contact to substrate capacitance, frequency of operation, load impedance connected to receiver contact and inductance of bond wire connected to gnd. the complete model shown in fig4can be simulated using ADS. Contact pads are sealed as 2D objects. They are defined with finite conductivity boundaries. There is air box which enclose the substrate has radiation boundary condition which means that all waves will be absorbed. Here C<sub>sub1</sub> is equal to C<sub>sub2</sub> due to symmetry and represents the contact to substrate capacitance of contact

International Journal of Scientific & Engineering Research Volume 3, Issue 4, April-2012 ISSN 2229-5518

pads.  $R_{load}$  is the load resistance;  $L_{gnd}$  is the bond wire inductance is needed in order to provide an accurate model of real structure.  $R_{1g}$  and  $R_{2g}$  have same values as structure is symmetrical. Isolation of test structure is defined as:

$$I=20 \log (Vrev/Vinj) dB[2]$$

(1)

#### **5 RESULTS AND DISCUSSIONS**

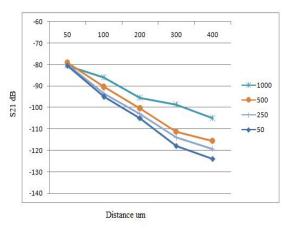

The HFSS simulation has been done using FEM technology, which is faster and accurate than Substrom and Spice. The isolation parameter S21 has been simulated for different substrate thicknesses by varying distance between two contacts. The resultant graph is deduced. The thickness is varied from 50 to  $1000\mu m$ .

Fig.5 Isolation vs distance graph for different thickness

Fig.5 shows that with decrease in thickness there is more reduction in crosstalk.

Distance um

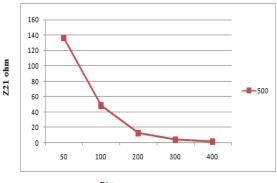

#### Fig.6 Impedance vs distance graph for thickness of $500 \mu m$

The  $Z_{21}$  values are obtained from the calibrated layer thicknesses and resistivities. For noise estimation purpose the values of  $R_{19}$  and  $R_{29}$  are important, so these are calculated using the values of  $Z_{11}$  and  $Z_{21}$  [7], where

$$Z_{11} = R_{1g} || (R_{12} + R_{2g})$$

(2)

$$Z21 = (R1g X R2g)/(R_{1g} + R_{12} + R_{2g}).$$

(3)

The Fig.6 shows that overall impedance decreases linearly at high frequencies with increase in distance between contacts. The impedance graph of substrate is evaluated for thickness 500 µm.

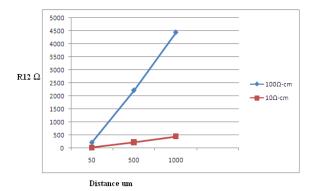

The resistance vs distance graph at different resistivities is shown in Fig.7 at 1 GHz frequency, which shows that for higher resistivity the resistance increases, with increase in distance.

Fig.7 Resistance vs distance for different resistivities

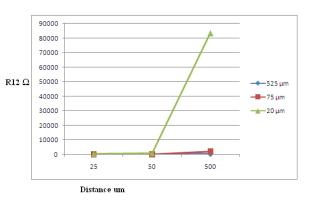

Fig.8 Resistance vs distance graph for different thicknesses

IJSER © 2012 http://www.ijser.org With more increase in distance, isolation starts becoming independent of distance. R<sub>12</sub> increases more rapidly with thinner substrates as shown in Fig.8 for Si substrate with 100ohm-cm resistivity and thickness is varied from  $20\mu m$  to  $525\mu m$ . Isolation increases with thinner substrate and it also improves with increasing the substrate resistivity. Isolation is related to distance between contacts to certain extent Distance driven isolation saturates as distance gets larger than the areas of transmitter and receiver.

## REFERENCES

[1] S. Donnay and G. Gielen, "Substrate Noise Coupling in Mixed-Signal IC's", Norwell, MA: Kluwer, 2003.

[2] Ranjit Gharpurey and Robert G. Meyer, "Modeling and Analysis of Substrate coupling in Integrated Circuits", IEEE JOURNAL OF SOLID-STATE CIRCUITS, vol.31, no3, pp.344-353 March 1996.

[3] K.rajendran, J.B Johnson, S.Furkey, M.Kumar and S. Fischer, "Measurement and 3D Simulation of Substrate Noise Isolation and Resistance for Mixed Signal Applications", IEEE topical meeting on silicon monolithic integrated circuits in RF systems. 2004

[4] R. Gharpurey and R.G. Meyer, "Modeling and analysis of substrate coupling in IC's", in Proc. IEEE Custom-Integrated Circuit Conf., pp. 125–128, May 1995.

[5] Salman, E.; Jakushokas, R.; Friedman, E.G.; Secareanu, R.M.; Hartin, O.L, "Methodology for efficient substrate noise analysis in Large- Scale mixed signal circuit", IEEE Transactions on Very Large Scale Integration (VLSI) systems, Vol.17, pp.1405-1418, October 2009.

[6] Emre Salman, "Switching Noise and Timing Characteristics in Nano-scale Integrated Circuits" Doctorate thesis, 2009

[7] Ajit Sharma, Chenggang Xu, Wen Kung Chu,

Nishath K. Verghese, Terri S. Fiez, Kartikeya Mayaram, "A Perdictive Methodology for Accurate Substrate Parasitic Extraction", ICAS, Vol.5, pp.149-152, IEEE 2004 [8] N.Masoumi, M. I. Elmadry, S. Safavi-Naeini, H. Hadi, "A Novel Analytical for evaluation of Substrate Crosstalk in VLSI circuits", The First IEEE workshop on Electronic Design, Test and Application, pp.355-359, 2002

Mandeep Kaur is currently pursuing masters degree program in Electronics and Communication Engineering, E-mail: sandhu.mandeekaur@gmail.com

<sup>•</sup> Rajesh Mehra is currently pursuing P.Hd program in Electronics and Communication Engineering